# JAY MARKETING ASSOCIATES

Manufacturers Representatives

# ERIES HD46505 (CRTC)

# IT CONTROLLER

CHI

P.O. Box 521, 763 Wing St. Plymouth, Michigan, 48170

(313) 459-1200

# • FEATURES

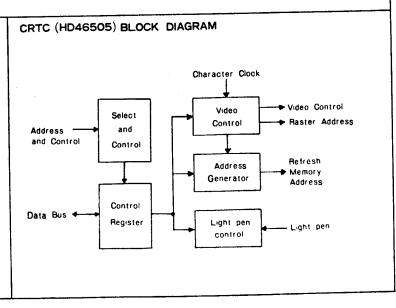

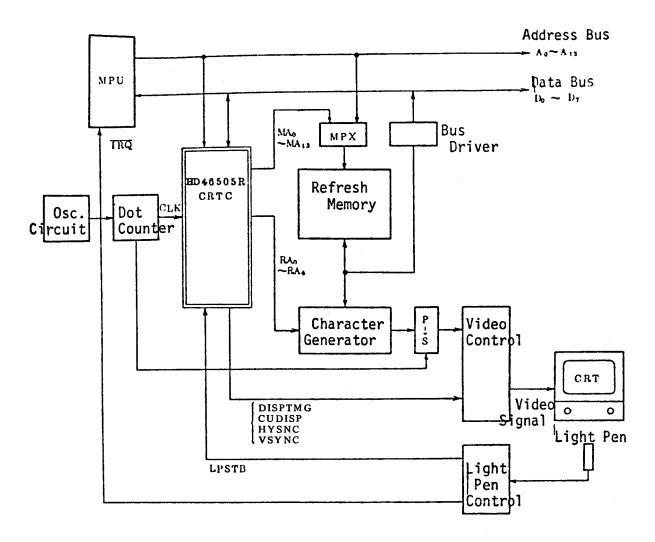

The HD46505 (CRTC) is a peripheral chip of HMCS6800 Microcomputer LSI families. It is designed in order to provide a simple and effective means of interfacing the raster scan CRT display to MPU bus. Its primary function is to generate the proper refresh address and video timings according to display format.

HD46505 is applicable to wide range of raster scan displays.

It is optimized for hardware/software balance in order to achieve integration of complex CRT interface functions and to maintain flexibility. Applications include intelligent CRT terminals, information display systems and video games.

- Programmable Screen and Character Format.

- Line Buffer-less Refreshing

- 14 Bits Refresh Memory Address

- Programmable Interface or Non-Interface Scan

- Cursor Control Function

- Programmable Cursor Format and its Blink

- Light Pen Detection Function

- · Limited or Full Graphic Display Capability

- Character by Character Video Control (Color, Blink, Inverse, etc.)

- Hardware Scrolling and Paging Functions

- No DMA Required, Refresh Memory is Time-multiplexed Between CRTC and MPU

- Directly Interfaceable to MPU Bus

- Single +5V Power Supply

- Directly TTL Compatible—All Inputs and Outputs

- N Channel E/D MOS Technology

- 40 Pin DIL Package

# BLOCK DIAGRAM HMCS 6800 SYSTEM BLOCK DIAGRAM MPU (HD46800) ROM (HN46830A) (HM46810A) (HD46821) ACIA (HD46850) CRTC CRT (HD46505) Address Bus Data Bus (16)(8)

HD46505R(CRTC) is an exclusive LSI controller to interface the microcomputer HD46800D and CRT display of raster scan type.

HD46505R(CRTC) is one of HMC6800 LSI family and has a perfect compatibility about the data line and control line with MPU (HD46800D).

The main function of CRTC is to generate necesary timing signals for a CRT dispaly of raster scan type according to the specification programmed by MPU. Therefore CRTC is applicable to very wide CRT displays such as a small size and low level character display, a large size and high level limited graphic display and raster type full graphic display by the designed feature, that is, programmable controller.

# • FUNCTIONS OF HD46505R (CRTC)

|                    | Item                                | Function of HD46505R (CRTC)                                                                                               | Remark                                                 |

|--------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

|                    |                                     | Horizontal scanning interval                                                                                              | Programmable by one character interval unit            |

|                    |                                     | Vertical scanning interval (Row unit)                                                                                     | Programmable by one row interval unit.                 |

|                    |                                     | Vertical scanning interval (Fine control)                                                                                 | Programmable by one raster unit.                       |

|                    |                                     | Displayed character number of one row                                                                                     |                                                        |

|                    | Programmable structure of a picture | Displayed character number of one picture                                                                                 |                                                        |

|                    |                                     | Raster number of one row                                                                                                  | Vertical dot number of one character + row space       |

|                    |                                     | Horizontal displayed position on CRT                                                                                      | Possible by programming the output timing of           |

|                    |                                     | Vertical displayed position on CRT                                                                                        | synchronous signals.                                   |

| Function of CRTC   |                                     | Pulse width of the horizontal synchronous signal                                                                          |                                                        |

|                    |                                     | Displayed position of cursor on a picture                                                                                 | Internal cursor register of 14 bit                     |

|                    | Programmable                        | Cursor format                                                                                                             |                                                        |

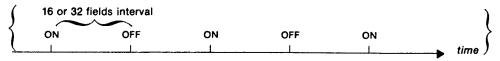

|                    | Cursor Display                      | Cursor blink and its cycle                                                                                                | Blink cycle is selectable one of 16 or 32 frame cycle. |

|                    |                                     | Non interlace mode                                                                                                        | Selectable one of these three                          |

|                    | Scan mode                           | Interlace sink mode                                                                                                       | modes.                                                 |

|                    |                                     | Interlace sink and video mode                                                                                             |                                                        |

|                    | Light Pen                           | Internal light pen register of 14 bit                                                                                     |                                                        |

|                    | Addressing of refresh memory        | Put out the refresh memory address of 14 bit                                                                              | Accessable refresh memory of 16K words max.            |

|                    | Programmable start address          | Internal start address register of 14 bit (Able to determine the display start address on the refresh memory by program.) | Operations such as paging, scrolling etc. are usable.  |

|                    | Power supply                        | Single +5V                                                                                                                |                                                        |

| LSI Structure      | Bus function                        | Directly connectable with HMCS6800 HMCS6800 family.                                                                       |                                                        |

| of CRTC            | Process                             | N channel Si gate E/D MOS                                                                                                 |                                                        |

|                    | Operation                           | Perfect static circuit                                                                                                    |                                                        |

|                    | Package                             | 40 pin Dual In Line type                                                                                                  |                                                        |

| CRTC Expandability |                                     | Character display                                                                                                         | Alpha numeric character and other character            |

|                    |                                     | Limited (simple type) graphic display                                                                                     | Graphic display                                        |

|                    |                                     | Full graphic display                                                                                                      | (Raster scan type)                                     |

|                    |                                     | Color display, Blink of displayed character                                                                               |                                                        |

|                    |                                     | Cluster control                                                                                                           |                                                        |

# • FUNCTIONS OF SIGNAL LINE

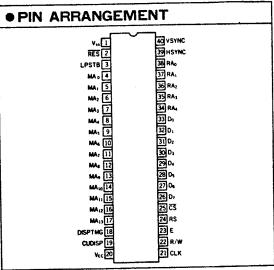

Internal signals of HD46505R (CRTC) are composed of 13 interface signals with MPU and 25 interface signals with CRT display.

### . INTERFACE SIGNAL WITH MPU

Bidirectional Data Bus ( $D_0 \sim D_7$ )

Bidirectional data bus  $(D_0 \sim D_7)$  are used for the data transfer between CRTC and MPU. Data bus output is a three state buffer and is in high impedance state except that MPU reads the data of CRTC.

#### READ/WRITE (R/W)

Read/Write Signal (R/W) controls the direction of data transfer between MPU and CRTC, that is, the data of CRTC is transferred to MPU while R/W is in "High" level and the data of MPU is transferred to CRTC while R/W is in "Low" level.

#### CHIP SELECT (CS)

Chip select signal ( $\overline{CS}$ ) is a signal to address CRTC chip and MPU can execute the operation of read/write to the internal registers of CRTC only when  $\overline{CS}$  is in "Low" level. Normally this signal is obtained by decoding the address signals of MPU under the condition that VMA signal of MPU is in "High" level.

#### • REGISTER SELECT (RS)

Register select signal (RS) is used for separating internal registers into one address register and 18 control registers, that is, the address register is selected while RS is in "Low" level and control register are selected while RS is in "High" level.

Normally the LSB of MPU's address bus (A<sub>0</sub>) is used for this signal.

#### • ENABLE (E)

Enable signal (E) is used for a strobe signal when MPU read or writes internal registers of CRTC. Normally  $\phi_2$  clock of MPU is used for this signal.

#### Reset (RES)

Reset signal (RES) is an input signal to reset CRTC externally. Internal states of CRTC become as follows when RES becomes "Low" level.

- 1) Internal counters of CRTC are all cleared and stopped their operations.

- 2) All output signals of CRTC become "Low" level.

- 3) Internal address register and control registers of CRTC keep former states regardless of RES.

This signal has difference functions from that of HMCS6800 family LSIs and its remarks are as follows.

- 1) RES signal is usable as reset signal only when LPSTB signal is in "Low" level.

- Output signals of MA<sub>0</sub> ~ MA<sub>13</sub>, RA<sub>0</sub> ~ RA<sub>4</sub> become "Low" level synchronizing with the "Low" level of CLK signal after RES becomes a "Low" level.

(CLK signal is necessary at least one cycle in order to make those output signals "Low" level.)

3) CRTC starts display operation immediately after RES becomes from "Low" level to "High" level and reset is canceled.

# ■ INTERFACE SIGNAL WITH CRT DISPLAY EQUIPMENT

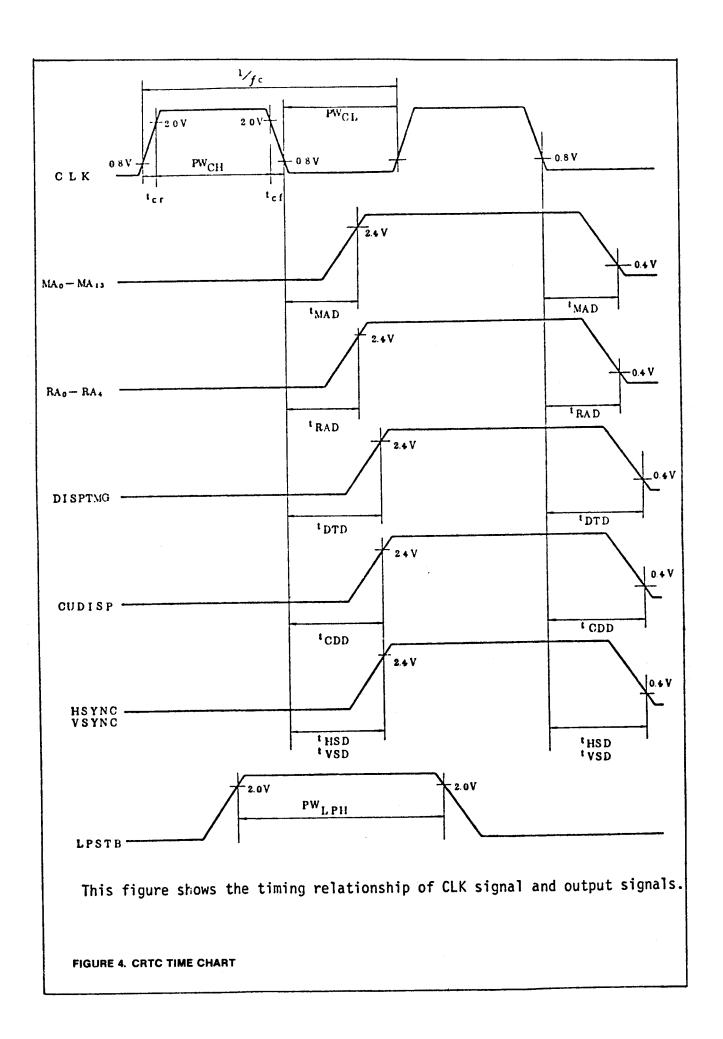

### • CHARACTER CLOCK (CLK)

Character clock signal (CLK) is used for a standard clock of CRTC's internal operation. This signal is given by the external high speed dot timing logic.

# HORIZONTAL SYNCHRONIZATION (HSYNC)

Horizontal synchronization signal (HSYNC) is used as a driving signal of horizontal deflection circuit of CRT display equipment.

Pulse width of vertical synchronization signal is fixed to 16 rasters cycle.

#### . DISPLAY TIMING (DISPTMG)

This signal is a signal which shows picture display interval of horizontal and vertical deflection. Video signal has to be sent to CRT display equipment only while this signal is in "High" level.

### • REFRESH MEMORY ADDRESS (MA<sub>0</sub> ~ MA<sub>13</sub>)

Refresh memory address ( $MA_0 \sim MA_{13}$ ) is used for memory address to refresh the displayed picture on CRT display equipment at a constant cycle. Address of 16K words (0 ~ 16383) max. can be designated by this address signal. Therefore paging to 8 pages is possible, for instance, in case of the display equipment of 2000 characters.

#### RASTER ADDRESS (RA₀ ~ RA₄)

Raster address ( $RA_0 \sim RA_4$ ) is used for a raster select signal of character generator and pattern generator.

#### CURSOR DISPLAY (CUDISP)

Cursor display signal (CUDISP) is a video signal to display the cursor on CRT display equipment. This signal is inhibited while DISPTMG is in "Low" level. Normally this signal is mixed with character video signal and sent to CRT display equipment.

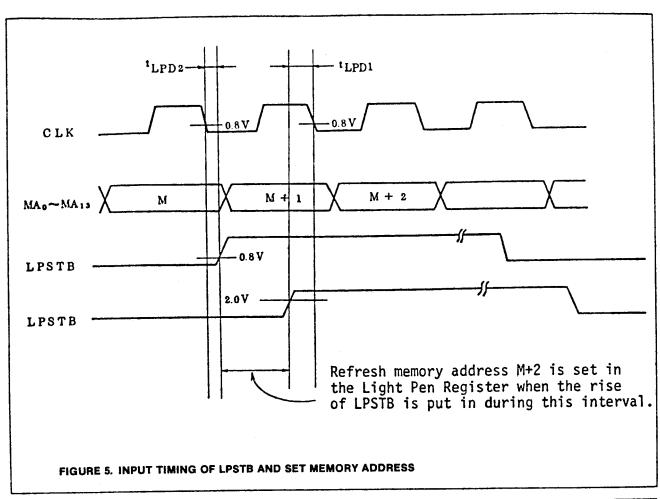

#### • LIGHT PEN STROBE (LPSTB)

Light pen strobe signal (LPSTB) is the detected pulse of character from the light pen. The content of refresh memory address ( $MA_0 \sim MA_{13}$ ) shown in Fig. 5 is set in the light pen register of 14 bit when this signal is put in. Memory address being set should be compensated by software for a delay time between display equipment and light pen and its control circuit.

# Internal Registers of HD46505R (CRTC)

| CS | D.C. | Address Reg. | Register |                                             | Program   |      |       |               | D                      | ata     | Bit |     |   |       |

|----|------|--------------|----------|---------------------------------------------|-----------|------|-------|---------------|------------------------|---------|-----|-----|---|-------|

| CS | RS   | 4 3 2 1 0    | No.      | Register Name                               | Unit      | READ | WRITE | 7 6           | 5                      | 4       | 3 2 | 2 1 | 0 | Notes |

| i  | X    | XXXXX        |          | Invalid                                     |           | _    |       |               | N                      | V       | 1   |     | N |       |

| 0  | 0    | XXXXX        | AR       | Address Req.                                |           | х    |       | M             | N                      |         |     | T   | П |       |

| 0  | 1    | 00000        | R0       | Horizontal total character number           | Character | Х    | 0     |               |                        |         |     |     |   | 1, 7  |

| 0  | 1    | 00001        | R1       | Horizontal displayed character number       | ditto     | х    | 0     |               |                        |         |     |     |   |       |

| 0  | 1    | 00010        | R2       | Position of<br>horizontal<br>sync. pulse    | ditto     | X    | 0     |               |                        |         |     |     |   | 7     |

| 0  | 1    | 00011        | R3       | Pulse width of<br>horizontal<br>sync. pulse | ditto     | X    | 0     | $\mathbb{N}$  | $\left  \cdot \right $ | V       |     |     |   |       |

| 0  | 1    | 00100        | R4       | Vertical total character number             | Line      | х    | 0     | N             |                        |         |     |     |   | 7     |

| 0  | 1    | 00101        | R5       | Total raster adjust                         | Raster    | X    | 0     |               | N                      |         |     | Τ   |   |       |

| 0  | 1    | 00110        | R6       | Vertical displayed character number         | Line      | х    | 0     | N             |                        |         |     |     |   | 2     |

| 0  | 1    | 00111        | R7       | Position of vertical sync. pulse            | ditto     | X    | 0     | N             |                        |         |     |     |   | 7     |

| 0  | 1    | 0 1 0 0 0    | R8       | Interlaced mode                             |           | X    | 0     | M             | N                      | V       | V   | V   | S | 3     |

| 0  | 1    | 01001        | R9       | Maximum raster raster                       | Raster    | Х    | 0     | M             | $\bigvee$              |         |     |     |   | 4, 7  |

| 0  | 1    | 01010        | R10      | Cursor start raster                         | ditto     | X    | 0     | В             | P                      |         |     |     |   | 5, 6  |

| 0  | 1    | 01011        | R11      | Cursor end raster                           | ditto     | X    | 0     | $\mathcal{N}$ | $\square$              |         |     |     |   | 6     |

| 0  | 1    | 01100        | R12      | Start address (H)                           |           | X    | 0     |               |                        |         |     |     |   |       |

| 0  | 1    | 0 1 1 0 1    | R13      | Start address (L)                           |           | X    | 0     |               |                        | $\prod$ |     |     |   |       |

| 0  | 1    | 01110        | R14      | Cursor (H)                                  |           | 0    | 0     | $\mathcal{N}$ |                        |         | I   |     |   |       |

| 0  | 1    | 01111        | R15      | Cursor (L)                                  |           | 0    | 0     |               |                        |         | I   |     |   |       |

| 0  | 1    | 10000        | R16      | Light Pen (H)                               |           | 0    | X     |               | $\prod$                |         |     |     |   |       |

| 0  |      | 10001        | R17      | Light Pen (L)                               |           | 0    | X     |               |                        |         |     |     |   |       |

Notes:

- 1. Set data should be odd in case of interlaced mode (R8 = 1 or 3).

- 2. Set data should be N/2 (N is a real displayed row number) when R8 = 3.

- 3. V designates video mode when S = 1. S designates interlaced mode.

- 4. Set data should be odd in case of R8 = 3.

- 5. B designates cursor blink and P designates blink cycle.

- 6. Combination of start raster and end raster should be (odd-odd) or (even-even) when R8 = 3.

- 7. (Set data) = (Designated data) -1.

- \*: 0 ......" "Low" level, 1 ....." "High" level

#### • INTERLACE MODE

| V      | S      | Mode                                              |

|--------|--------|---------------------------------------------------|

| 0<br>1 | 0      | Non interlace mode                                |

| 0<br>1 | 1<br>1 | Interlace sink mode Interlace sink and video mode |

#### • CURSOR DISPLAY

| В | P   | Cursor Display Mode                               |

|---|-----|---------------------------------------------------|

| 0 | 0   | Cursor doesn't blink.                             |

| 0 | 1   | Cursor isn't displayed.                           |

| 1 | . 0 | Cursor blinks by the cycle of 16 fields interval. |

| 1 | 1   | Cursor blinks by the cycle of 32 fields interval. |

# • RESTRICTIONS ON PROGRAMMING OF HD46505R (CRTC)

- 1)  $0 < Nhd < Nht + 1 \le 256$

- 2) Nht: Odd number (When interlace sink or interlace sink and video mode)

- 3)  $0 < Nvd < Nvt + 1 \le 128$

- 4) Nhsp + Nhsw < Nht + 1

- 5) Nvsp ≤ Nvt

- 6)  $0 \le N_{CSTART} \le N_{CEND} \le Nr$

- 7) One of next two cases should be selected in case of interlace sink and video mode

- i. N<sub>CSTART</sub>, N<sub>CEND</sub> are both even.

- ii. N<sub>CSTART</sub>, N<sub>CEND</sub> are both odd.

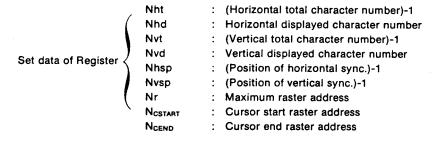

Meanings of symbols mentioned above.

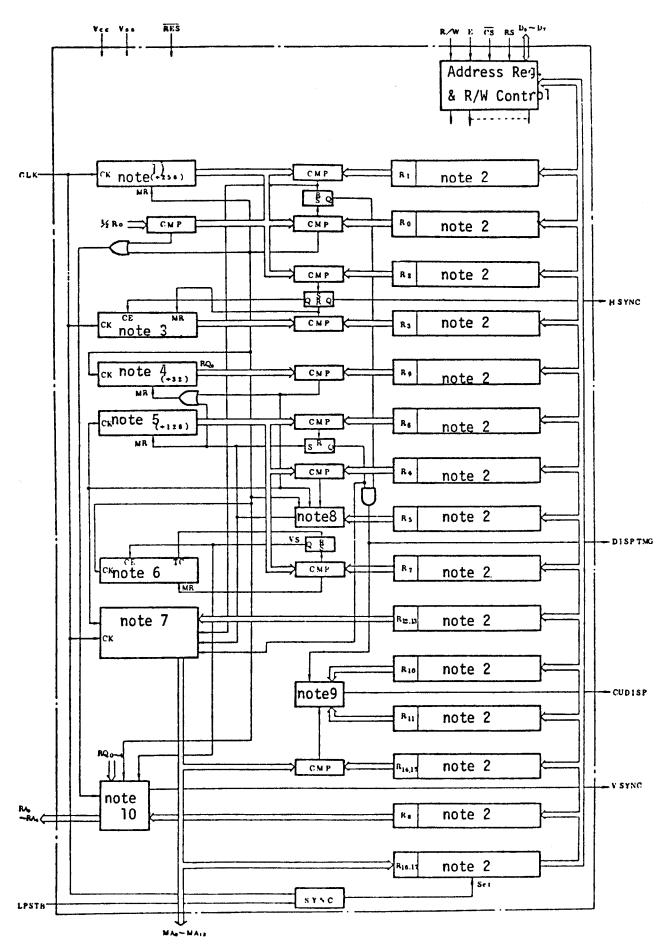

FIGURE 1. INTERNAL BLOCK DIAGRAM OF HD46505R (CRTC)

Notes:

- 1. Character Counter

- 2. Register names are as follows:

| Register Number | Register Name                              |

|-----------------|--------------------------------------------|

| R0              | Horizontal Total Character Number Reg.     |

| R1              | Horizontal Displayed Character Number Reg. |

| R2              | Horizontal Synchronizing Position Reg.     |

| R3              | H. Synchronous Pulse Width Reg.            |

| R4              | Vertical Total Character Number Reg.       |

| R5              | Total Raster Adjust Reg.                   |

| R6              | Vertical Displayed Character Number Reg.   |

| R7              | V. Synchronous Position Reg.               |

| R8              | Interlace Mode Reg.                        |

| R9              | Maximum Raster Address Reg.                |

| R10             | Cursor Start Raster Reg.                   |

| R11             | Cursor End Raster Reg.                     |

| R12             | Start Address (H) Reg.                     |

| R13             | Start Address (L) Reg.                     |

| R14             | Cursor (H) Reg.                            |

| R15             | Cursor (L) Reg.                            |

| R16             | Light Pen (H) Reg.                         |

| R17             | Light Pen (L) Reg.                         |

|                 |                                            |

- 3. H. Synchronous Pulse Width Counter

- 4. Raster Counter

- 5. Line Counter

- 6. V. Synchronous Pulse Width Counter

- 7. Linear Address Generator

- 8. V. total Controller

- 9. Cursor Controller

- 10. Interlace Controller

# **MAXIMUM RATINGS**

| Item                  | Symbol | Value      | Unit |

|-----------------------|--------|------------|------|

| Supply Voltage*       | Vcc    | -0.3 ~ 7.0 | v    |

| Input Voltage*        | Vin    | -0.3 ~ 7.0 | V    |

| Operating Temperature | Topr   | -20 ~ 75   | °C   |

| Storage Temperature   | Tsig   | -55 ~ 150  | °C   |

<sup>\*</sup>In respect to Vss (GND).

### NOTE)

Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

# ■ RECOMMENDED OPERATING CONDITIONS

| Item                  | Symbol                             | min.        | typ.    | max.              | Unit   |

|-----------------------|------------------------------------|-------------|---------|-------------------|--------|

| Supply Voltage*       | Vcc                                | 4.75        | 5       | 5.25              | v      |

| Input Voltage*        | V <sub>IL</sub><br>V <sub>IH</sub> | -0.3<br>2.0 | <u></u> | 0.8<br><i>Vcc</i> | v<br>v |

| Operating Temperature | Topr                               | -20         | 25      | 75                | °C     |

<sup>\*</sup>In respect to Vss (GND).

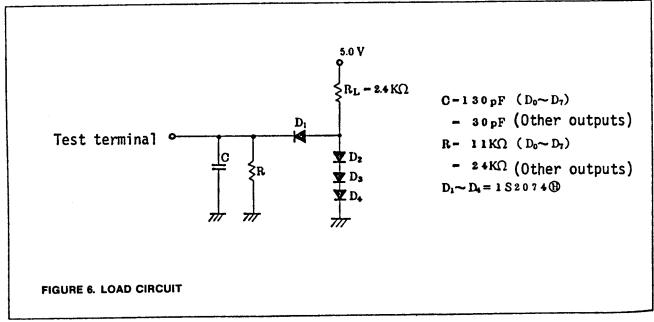

# • ELECTRICAL CHARACTERISTICS ( $Vcc = 5V \pm 5\%$ , Vss = 0V, $Ta = -20 \sim 75^{\circ}C$ )

| Item                               |                               | Symbol | Test Condition                             | min. | typ.* | max. | Unit |

|------------------------------------|-------------------------------|--------|--------------------------------------------|------|-------|------|------|

| Input "High" Level<br>Voltage      | All Inputs                    | Vih    |                                            | 2.0  |       | Vcc  | V    |

| Input "Low" Level<br>Voltage       | All Inputs                    | VIL    |                                            | -0.3 |       | 0.8  | V    |

| Input Leak Current                 | Inputs without $D_0 \sim D_7$ | IIN    | $V_{IN} = 0 \sim 5.25 \text{V}$            | _    | 1.0   | 2.5  | μΑ   |

| Input Current at Three state (OFF) | $D_0 \sim D_7$                | Itsi   | VIN = 0.4 ~ 2.4V                           |      | 2.0   | 10   | μА   |

| Output "High" Level                | $D_0 \sim D_7$                | Von    | ILOAD = -205μA                             | 2.4  |       |      | v    |

| Voltage                            | Other outputs                 | 70"    | ILOAD = -100μA                             | 2.4  |       |      |      |

| Output "Low" Level<br>Voltage      | All Outputs                   | Vol    | <i>ILOAD</i> = 1.6mA                       | _    |       | 0.4  | v    |

| Input Capacitance                  | $D_0 \sim D_7$                | CIN    | $V_{IN} = 0$ V, $T_a = 25$ °C,             | _    |       | 12.5 | pF   |

|                                    | Other Inputs                  |        | f = 1MHz                                   |      |       | 10.0 | pF   |

| Output Capacitance                 |                               | Cout   | $V_{IN} = 0$ V, $T_a = 25$ °C,<br>f = 1MHz | _    | _     | 10.0 | pF   |

| Power Dissipation                  |                               | Po     |                                            | T -  | 600   | 1000 | mW   |

<sup>\*</sup>Value at  $T_a = 25^{\circ}$ C,  $V_{CC} = 5$ V.

# • TIMING CHARACTERISTICS

Control Signal Timing of CRTC

| Item                                         |              | Symbol           | Test Condition | min. | typ. | max.         | Unit |

|----------------------------------------------|--------------|------------------|----------------|------|------|--------------|------|

| Clock Frequency                              |              | fc               | Fig. 4         |      | _    | 3.0          | MHz  |

| Clock Pulse Width                            | "Low" Level  | PWc1             | Fig. 4         | 150  | _    | _            | ns   |

| Clock Fulse Width                            | "High" Level | РWсн             | Fig. 4         | 150  | _    |              | ns   |

| Rise/Fall Time of Clock Input                |              | ter<br>tef       | Fig. 4         |      |      | 15           | ns   |

| Memory-Address Delay Time                    |              | tmad             | Fig. 4         | _    | _    | 160          | ns   |

| Raster-Address Delay Time                    |              | 1RAD             | Fig. 4         | _    | _    | 160          | ns   |

| Display-Timing Delay                         | Гime         | t <sub>DTD</sub> | Fig. 4         | T -  |      | 250          | ns   |

| H. Sync. Delay Time                          |              | thsd             | Fig. 4         |      |      | 250          | ns   |

| V. Sync. Delay Time                          |              | tvsD             | Fig. 4         | _    |      | 250          | ns   |

| Cursor Display Delay                         | l'ime        | <b>t</b> CDD     | Fig. 4         |      | _    | 250          | ns   |

| Pulse Width of Light Pen Strobe              |              | PWLPH            | Fig. 4         | 80   |      | <del>-</del> | ns   |

| Uncertain Time of Light Pen Strobe Receiving |              | <b>t</b> LPD1    | Fig. 5         |      | ] _  | 80           | ns   |

|                                              |              | tlPD2            | Fig. 5         | _    | _    | 10           | ns   |

# • BUS TIMING CHARACTERISTICS

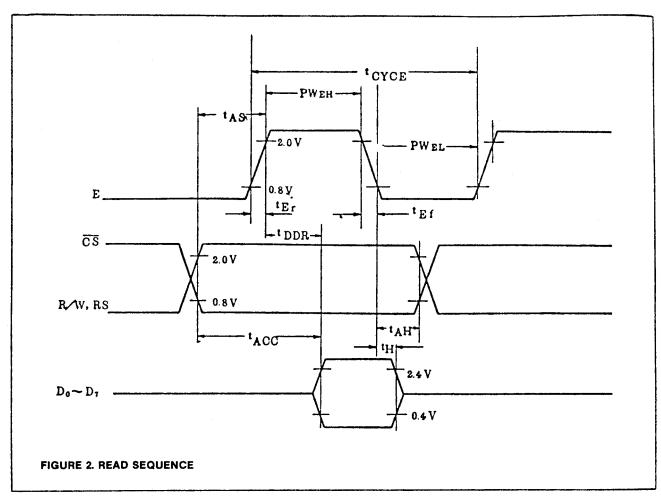

### • READ SEQUENCE

| Item                           |              | Symbol                  | Test Condition | min. | typ.     | max. | Unit |

|--------------------------------|--------------|-------------------------|----------------|------|----------|------|------|

| Enable Cycle Time              |              | <i>t</i> cyce           | Fig. 2         | 1.0  | _        | _    | μs   |

| Enable Pulse Width             | "High" Level | PW <sub>EH</sub>        | Fig. 2         | 0.45 | T        | _    | μs   |

| Enable Pulse Width             | "Low" Level  | PWEL                    | Fig. 2         | 0.40 |          | _    | μs   |

| Setup Time of ADDRESS-ENABLE   |              | tas                     | Fig. 2         | 140  |          |      | ns   |

| Data Delay Time                |              | <b>t</b> DDR            | Fig. 2         | T    |          | 320  | ns   |

| Data Hold Time                 |              | tн                      | Fig. 2         | 10   | <u> </u> |      | ns   |

| Rise/Fall Time of Enable Input |              | t <sub>E</sub> -        | Fig. 2         | _    | _        | 25   | ns   |

| Address Hold Time              |              | <i>t</i> <sub>A</sub> H | Fig. 2         | 10   |          | _    | ns   |

| Data Access Time               |              | tacc                    | Fig. 2         |      | T —      | 460  | ns   |

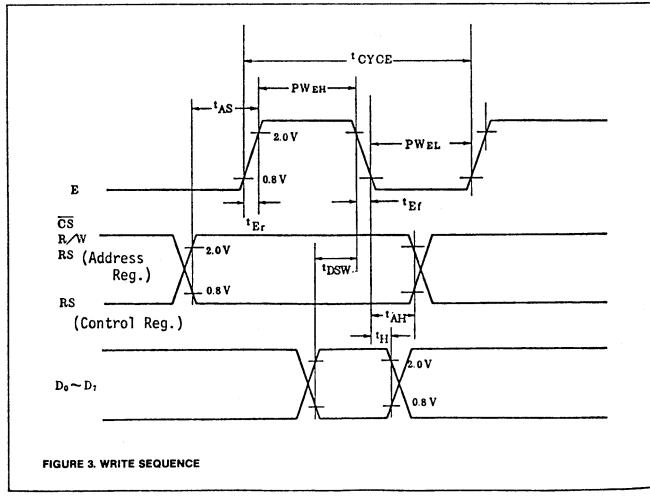

# • WRITE SEQUENCE

| Item                           |              | Symbol        | Test Condition | min. | typ. | max.     | Unit |

|--------------------------------|--------------|---------------|----------------|------|------|----------|------|

| Enable Cycle Time              |              | <b>I</b> CYCE | Fig. 3         | 1.0  | _    |          | μs   |

| Enable Pulse Width             | "High" Level | PWEH          | Fig. 3         | 0.45 |      | T -      | μs   |

| Enable Pulse Width             | "Low" Level  | PWEL          | Fig. 3         | 0.40 | T    | <b>—</b> | μs   |

| Setup Time of ADDRESS-ENABLE   |              | tas           | Fig. 3         | 140  | _    |          | ns   |

| Data Setup Time                |              | tosw          | Fig. 3         | 195  |      | _        | ns   |

| Data Hold Time                 |              | tн            | Fig. 3         | 10   |      |          | ns   |

| Rise/Fall Time of Enable Input |              | to<br>tej     | Fig. 3         |      | _    | 25       | ns   |

| Address Hold Time              |              | tah -         | Fig. 3         | 10   | _    |          | ns   |

FIGURE 7. CHARACTER DISPLAY SYSTEM EXAMPLE USING HD46505R (CRTC)